Konzeptionierung und Hardwaredesign eines Hardware-in-the-Loop-Systems für einen Modularen-Multilevel-Umrichter

- Forschungsthema:Hardware in the Loop

- Typ:Masterarbeit

- Datum:Oktober 2024 bis April 2024

- Betreuung:

- Bild:

- Bearbeiter:

Jannik Bitterle

-

Motivation

Das Stromnetz befindet sich im Wandel von einer zentralisierten hin zu einer dezentralisierten Energieversorgung durch die steigende Anzahl erneuerbarer Energiequellen. Eine zentrale Herausforderung ist die Netzstabilität angesichts fluktuierender erneuerbarer Energiequellen. Hier kommen Netzkupplungen mit leistungselektronischen Umrichtern ins Spiel, welche zur Stabilisierung des Netzes eingesetzt werden sollen.

Damit diese Umrichter unter Realbedingungen untersucht werden können, entsteht am Campus Nord das High Power Grid Lab (HPGL), welches eine kontrollierte Testumgebung für Umrichter im MW-Bereich zur Verfügung stellt. Das HPGL selbst besteht aus mehreren Modularen Multilevel Umrichtern (MMC), welche in verschiedenen Konfigurationen miteinander verschaltet werden können und so das reale Stromnetz nachbilden.

Um das Verhalten des HPGL bereits vorab zu testen, wird ein skalierter Demonstrator bestehend aus drei MMCs mit jeweils 192 Zellen am ETI aufgebaut.

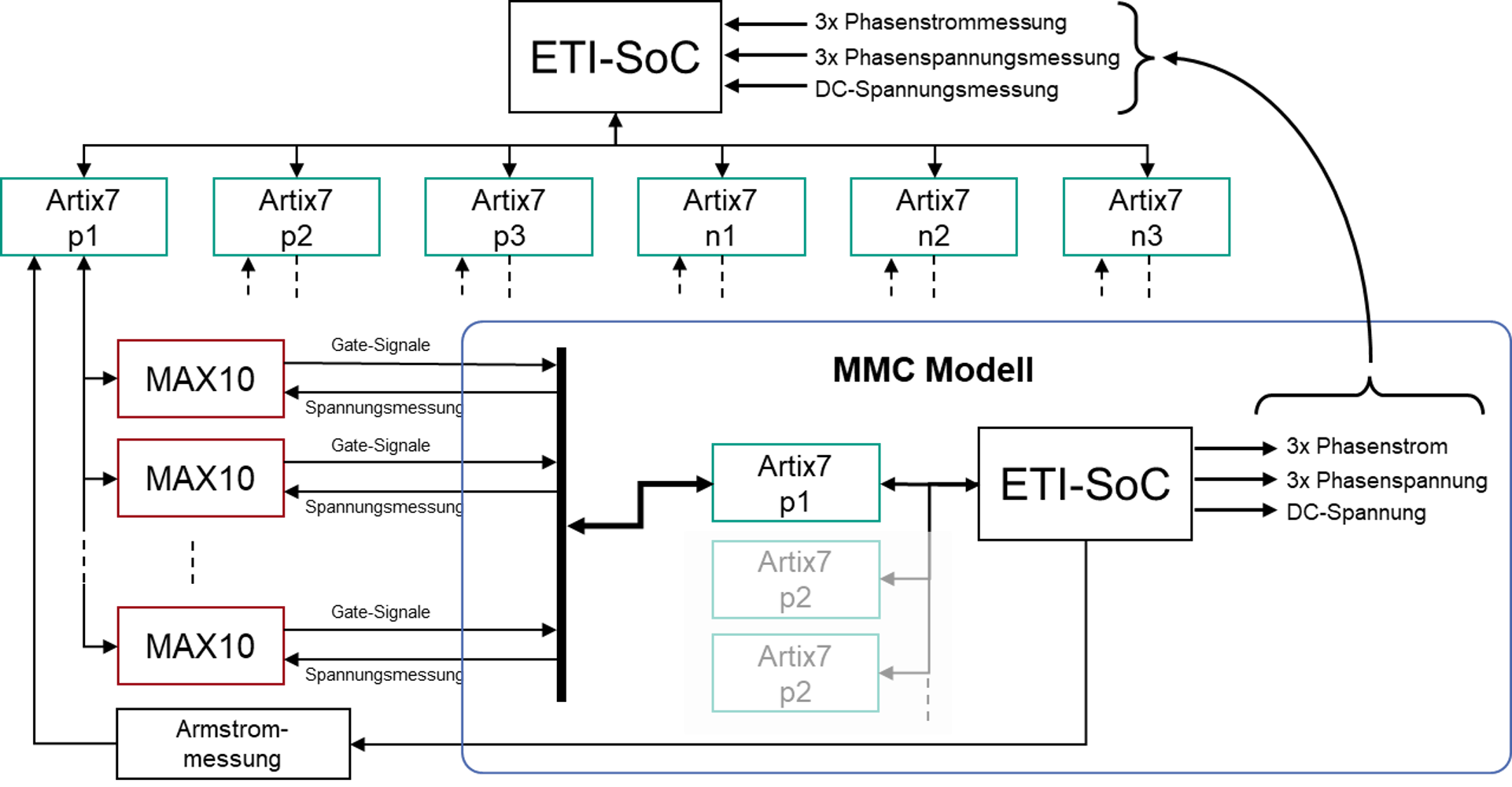

Zur Parallelisierung im Entwicklungsprozess und um MMC-Regelstrategien auf Signalebene zu testen, soll zusätzlich ein MMC mit Hilfe eines Hardware-in-the-Loop-(HiL)-System nachgebildet werden.

Aufgabenstellung

Diese Arbeit beschäftigt sich mit der Entwicklung und dem Aufbau eines HiL-Systems für einen der Demonstrator-MMCs. Der Fokus liegt dabei auf dem Entwurf des Gesamtsystems, bestehend aus der Signalverarbeitung der MMC-Ansteuerung sowie der Signalverarbeitung für die Echtzeitmodellierung des MMCs. Im ersten Teil des Hardwaredesigns soll die Schnittstelle entworfen werden, welche es ermöglicht die Signalverarbeitung des MMCs in das HiL zu integrieren. Parallel dazu erfolgt der Entwurf der Signalverarbeitungshardware, basierend auf dem ETI-SoC-System, welche für die Echtzeitsimulation des MMC-Modells verwendet werden soll.

Aufgrund der hohen Zellenzahl des MMCs muss die Implementierung des HiL-Systems über mehrere FPGAs sowie den ARM-Kern des SoC-Systems erfolgen. Zum Abschluss der Arbeit soll die entworfene Hardware in Betrieb genommen werden und eine erste Kommunikation zwischen den FPGAs aufgebaut werden.