Design und Implementierung einer synchronen Pulsweitenmodulation für 2-Level und 3-Level Wechselrichter auf einem FPGA

- Forschungsthema:Adaptive Modulation

- Typ:Bachelorarbeit

- Datum:05/2025

- Betreuung:

M.Sc. Rainer Pfeffer

- Bild:

- Bearbeiter:

vergeben

-

Motivation

Die Elektrifizierung des Schienenverkehrs auf nichtelektrifizierten Strecken erfolgt zunehmend durch den Einsatz batteriebetriebener Fahrzeuge. Diese Entwicklung stellt höhere Anforderungen an die Energieeffizienz des gesamten Antriebssystems. Insbesondere der Umrichter als zentrales Bindeglied zwischen Energiequelle und Elektromotor hat hierbei einen signifikanten Einfluss auf Wirkungsgrad und Systemverhalten. Dessen Effizienz hängt sowohl von der verwendeten Topologie als auch von der eingesetzten Taktfrequenz ab. Die systematische Analyse und Optimierung synchroner Taktungsstrategien ermöglicht eine gezielte Reduktion von Schaltverlusten sowie eine Verbesserung der elektromagnetischen Verträglichkeit.

Aufgabenstellung

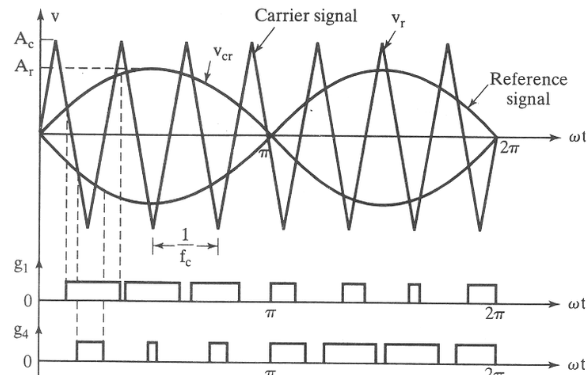

In der Arbeit soll die bestehende ETI-Bibliothek um Funktionalitäten zur synchronen Taktung für 2- und 3-Level-Umrichter erweitert werden. Ziel ist die Entwicklung eines modularen, parametrierbaren Taktgenerators, der sowohl in der Simulation als auch in der automatisierten HDL-Codegenerierung für Vivado einsetzbar ist. Hierfür ist ein geeignetes Interrupt-Timing-Konzept zu entwerfen und in Vivado umzusetzen. Die entwickelte Taktgenerierung wird anschließend im Labor an einem geeigneten Versuchsaufbau implementiert und hinsichtlich ihres Verhaltens mit einer bestehenden asynchronen Taktung verglichen.