Aufbau einer Hardware-in-the-Loop Testumgebung für die Local Control Unit eines Submoduls eines Modular Multilevel Converters

- chair:Modular Multilevel Converter

- type:Bachelor-/Masterarbeit

- time:ab sofort

- tutor:

- Image:

-

Motivation

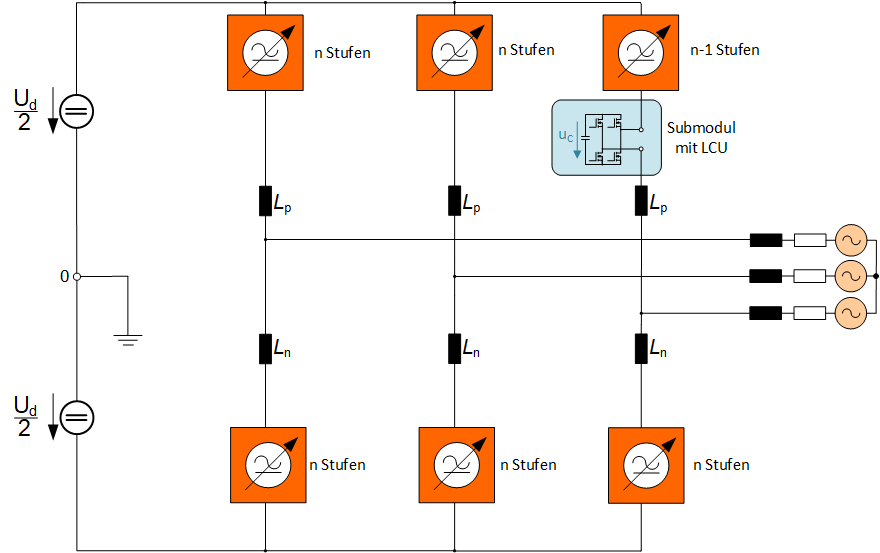

Im Stromnetz, insbesondere für die Hochspannungs-Gleichstromüber-tragung (HVDC) nehmen Modular Multilevel Converter (MMC) eine immer wichtigere Rolle ein. Der Vorteil von MMC ist ihr modulares Konzept, bestehend aus einer Vielzahl von Submodulen, die in Serie geschaltet werden. Dadurch werden eine hohe Zuverlässigkeit und Skalierbarkeit des Umrichters erreicht. Um ein korrektes Verhalten der Submodule im Gesamt-MMC-Verbund schon vor dem Komplettaufbau des MMC zu gewährleisten, ist es von Vorteil diese unter möglichst realistischen Bedingungen zu testen.

Ein Submodul besteht meist aus einem Leistungsteil und einer Local Control Unit (LCU), die einen Microcontroller oder FPGA beinhaltet, welche von der zentralen Regelung eine Sollspannung empfangen und daraus Gatesignale berechnen. In einer vorherigen Arbeit wurde bereits ein detailliertes HiL-Modell eines Vollbrücken-Submoduls entwickelt. In Zusammenspiel mit einer LCU und einem in einer anderen Arbeit entwickelten MMC-HiL-Modells kann die Interaktion zwischen LCU mit Submodul und MMC untersucht werden.

Aufgabenstellung

In dieser Arbeit soll eine HiL-Testumgebung für die LCU eines Submoduls eines Modularen Multilevel Converters entwickelt werden. Dafür soll im ersten Schritt eine Platine designt werden, die die Schnittstellen zu zwei verschiedenen LCU zur Verfügung stellt, sowie ein FPGA, welcher das HiL-Modell des Vollbrücken-Submoduls enthält. Im zweiten Schritt soll die Platine in Betrieb genommen werden. Danach soll die Platine mit dem SoC-System, dem ETI-eigenen Signalverarbeitungssystem, verbunden und in Kombination mit dem MMC-HiL-Modell getestet werden. Zum Abschluss können je nach Zeit und Interesse weitere Punkte, wie die Überarbeitung des MMC-HiL-Modells, die Erweiterung der Modelle auf Halb-brückenmodule oder die Auswirkung von Totzeit zwischen der Submodul-platine und dem MMC-HiL-Modell untersucht werden.