Optimierung und Implementierung des Remote System Upgrade für eine parallele FPGA‑Konfiguration in Modulare Multilevel Convertern

- chair:Signalverarbeitung

- type:Bachelorarbeit

- time:ab sofort

- tutor:

- Image:

- person in charge:

zu vergeben

-

Motivation

Das Stromnetz befindet sich im Wandel von einer zentralisierten hin zu einer dezentralisierten Energieversorgung durch die zunehmende Integration erneuerbarer Energiequellen. Die daraus resultierenden Anforderungen an Netzstabilität und Dynamik erfordern den Einsatz leistungsfähiger, leistungselektronischer Netzkopplungen. Zur experimentellen Untersuchung solcher Systeme entsteht am Campus Nord das High Power Grid Lab (HPGL), das eine kontrollierte Testumgebung für Umrichter im MW-Bereich bereitstellt. Das HPGL basiert auf mehreren Modularen Multilevel Umrichtern (MMC), die flexibel miteinander verschaltet werden können und so verschiedene Netzsituationen emulieren.

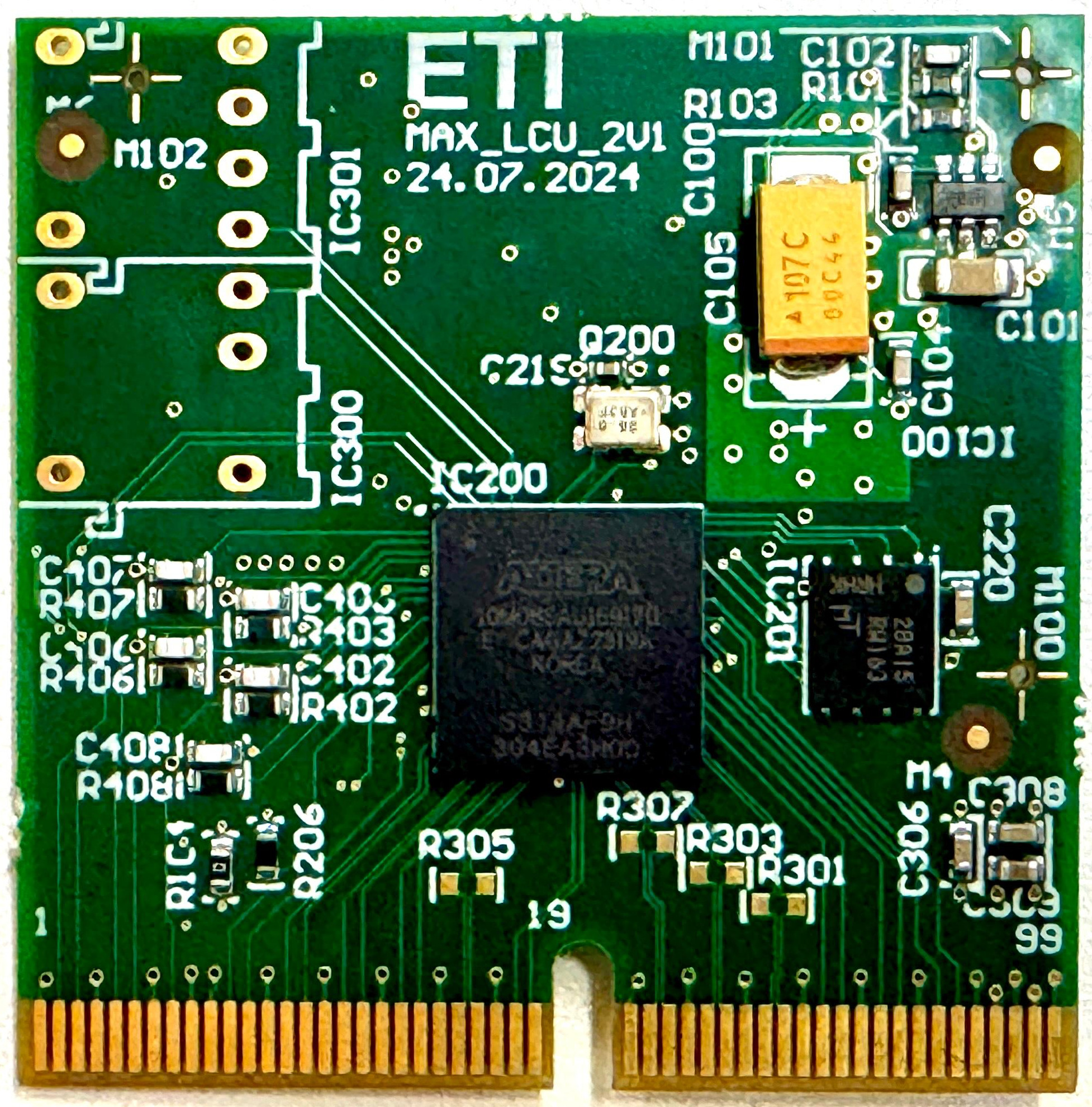

Zur Vorbereitung des HPGL wird am ETI ein Demonstrator aus drei MMCs aufgebaut. Jeder Umrichter besteht aus 192 Submodulen (SM), die neben der Leistungselektronik über eine Local Control Unit (LCU) mit einem MAX10-FPGA verfügen. Aufgrund dieser hohen Anzahl an FPGAs führt jede Designanpassung bei konventioneller Einzelprogrammierung zu einem erheblichen zeitlichen Aufwand. Das Remote System Upgrade (RSU) ermöglicht hingegen die Aktualisierung der Firmware der LCUs im eingebauten Zustand über die bestehende Signalverarbeitungsschnittstelle.

Aufgabenstellung

In einer vorangegangenen Arbeit wurde das Remote System Upgrade (RSU) für den MAX10‑FPGA über eine direkte UART‑Verbindung zwischen PC und FPGA grundlegend implementiert und validiert. Ziel der vorliegenden Arbeit ist es, diese Punkt‑zu‑Punkt‑Lösung in die interne Signalverarbeitungsarchitektur des MMC zu überführen und eine skalierbare, parallele Programmierung mehrerer LCUs zu ermöglichen.

Hierzu ist zunächst die bestehende RSU‑Implementierung auf dem MAX10‑FPGA zu analysieren und hinsichtlich ihrer Funktionalität und Effizienz zu optimieren. Anschließend soll die Übertragung des Konfigurations‑Images von der zentralen Steuereinheit (dem ETI‑SoC‑System) aus erfolgen. Auf dieser Basis ist ein geeignetes Gesamtkonzept für die Verwaltung und Übertragung der Images zu entwickeln und eine prototypische Lösung zur parallelen Programmierung mehrerer FPGAs zu realisieren. Abschließend ist die entwickelte Gesamtlösung auf der realen MMC‑Hardware experimentell zu validieren.