Dr.-Ing. Fabian Stamer

- Room: 111

- Phone: +49 721 608 46858

- Fax: +49 721 358854

- fabian stamer ∂does-not-exist.kit edu

- orcid.org/0000-0003-4663-1919

Karlsruher Institut für Technologie (KIT)

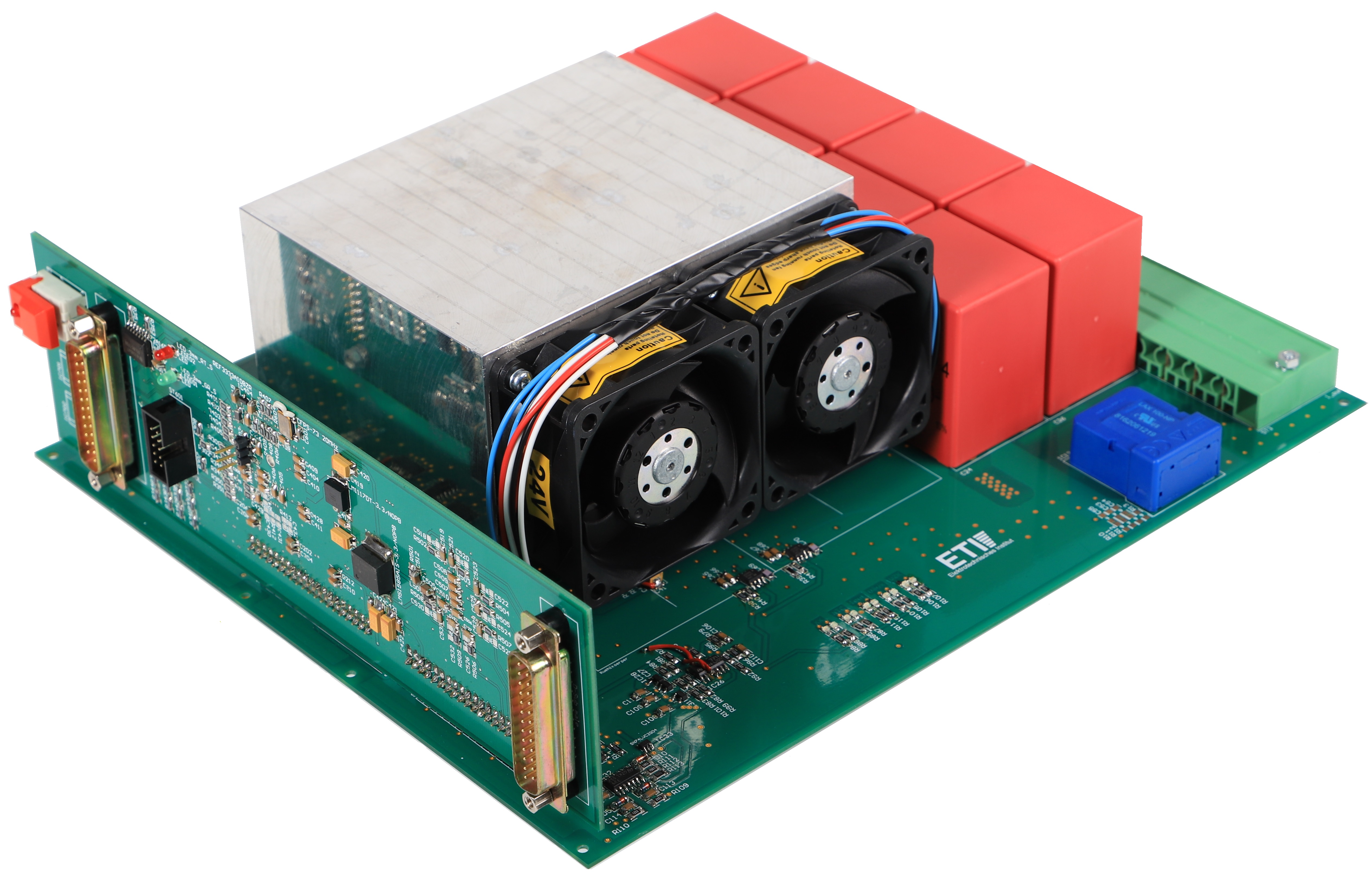

Elektrotechnisches Institut (ETI)KIT Campus Süd

Engelbert-Arnold-Str. 5

Geb. 11.10, Raum 111

D-76131 Karlsruhe

Intelligente Gate-Ansteuerung von Leistungshalbleitern

- Contact:

- Project Group:

Leistungselektronische Systeme (PES)

- Partner:

Siemens AG

| Title | Image | Source | Short Description |

|---|---|---|---|

| Short-Circuit Turn OFF Capability of an Adaptive Open Loop Gate Driver for Insulated Gate Bipolar Transistors | IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society |

This paper analyzes how a previously presentedadaptive open loop gate driver handles fault currents. Whencontrolling insulated gate bipolar transistors (IGBTs), it isessential to ensure safe operation in the whole operating range.Most important, the gate driver must be able to safely turn OFFa unacceptably high current like a short-circuit current. Such afault generates a current of unknown magnitude, which has tobe switched off as safe and slow as possible. A special shutdownmode of the investigated open loop gate driver is presented in thispaper, which makes it possible to safely shut down a fault currentwithout knowing the actual operating point of the IGBT. Basedon measurement results it is shown that all currents, includingdesaturation of the IGBT can be safely turned OFF. |

|

| Sensitivity analysis of an adaptive open loop gate driver to manufacturing related varying IGBT parameters | |||

| Prädiktive Gate-Ansteuerung zur Optimierung des Schaltverhaltens von IGBTs | Dissertation an der Fakultät für Elektrotechnik und Informationstechnik (ETIT) des Karlsruher Instituts für Technologie (KIT) KITopen-ID: 1000131089 DOI: 10.5445/IR/1000131089 |

||

| New Gate Driver for online adjustable switching behavior of Insulated Gate Bipolar Transistors (IGBTs) | 2019 21th European Conference on Power Electronics and Applications (EPE'19 ECCE Europe) |

This paper presents a new gate driver concept that allows an online, open-loop adjustment of the switching behavior of power semiconductors during operation. An inductive impedance instead of an ohmic impedance enables the required adjustable gate current and thus the desired gate voltage curve. The driver can individually adapt the switching behavior of the transistor to each individual switching edge. Thus for example the dv/dt and di/dt can be influenced, whereby the EMI behavior, the reverse recovery rate, the occurring overvoltage or the switching losses can also be influenced. The new gate driver was compared to a conventional resistive gate driver and the measurement results clearly show the advantages of the proposed driver concept. |

|

| Mirror Source based Overcurrent and Short Circuit Protection Method for High Power SiC MOSFETs | PCIM Europe digital days : : International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 3-7 May 2021 |

This paper presents a fast overcurrent and short circuit protection based on the mirror source detection method for 1200V/1200A Silicon Carbide (SiC) MOSFETs used in a high power Dual Active Bridge (DAB). It will be shown that this protection method is feasible for a low inductive short circuit caused by a half bridge shoot through, a high inductive short circuit based on a failure inside the load as well as short circuits of Type 1 or hard switching fault. Additionally, the short circuit behaviour is analyzed for different junction temperatures of the MOSFETs. Experimental results proof that using the investigated method always ensures the operation in the Short Circuit Safe operating Area (SCSOA) of the MOSFET after triggering short circuits. |

|

| Investigation of Different Balancing Methods for Modular 3-Level T-Type Voltage Source Converters with Distributed DC-Link Capacitors | 44rd Annual Conference of the IEEE Industrial Electronics Society (IECON) |

||

| A multi-dimensional full automatic power semiconductor test bench for accurate semiconductor loss calculation | PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management |

"This paper presents a multi-dimensional full automatic semiconductor test bench for accurate semiconductor |